【HDL】Verilog HDL仿真工具iverilog(Icarus Verilog)

Icarus Verilog官网:http://iverilog.icarus.com/1. iverilog的安装Linux/Ubuntu:官网给出的教程有点复杂,我试了一下直接用下面的命令就可以安装。sudo apt-get install iverilogsudo apt-get install gtkwave2. iverilog的IDE使用vscode+iverilog插件作为IDE。i

·

Icarus Verilog官网:http://iverilog.icarus.com/

1. iverilog的安装

Linux/Ubuntu:

官网给出的教程有点复杂,我试了一下直接用下面的命令就可以安装。

sudo apt-get install iverilog

sudo apt-get install gtkwave

2. iverilog的IDE

使用vscode+iverilog插件作为IDE。

iverilog插件,选择“mshr-h”这个作者创建的插件。

3.测试Demo

参考:https://www.bilibili.com/video/BV1Ef4y1X7wZ?from=search&seid=3262477841150114451

此Demo是演示“2输入与门”的仿真。仿真波形使用gtkwave工具。

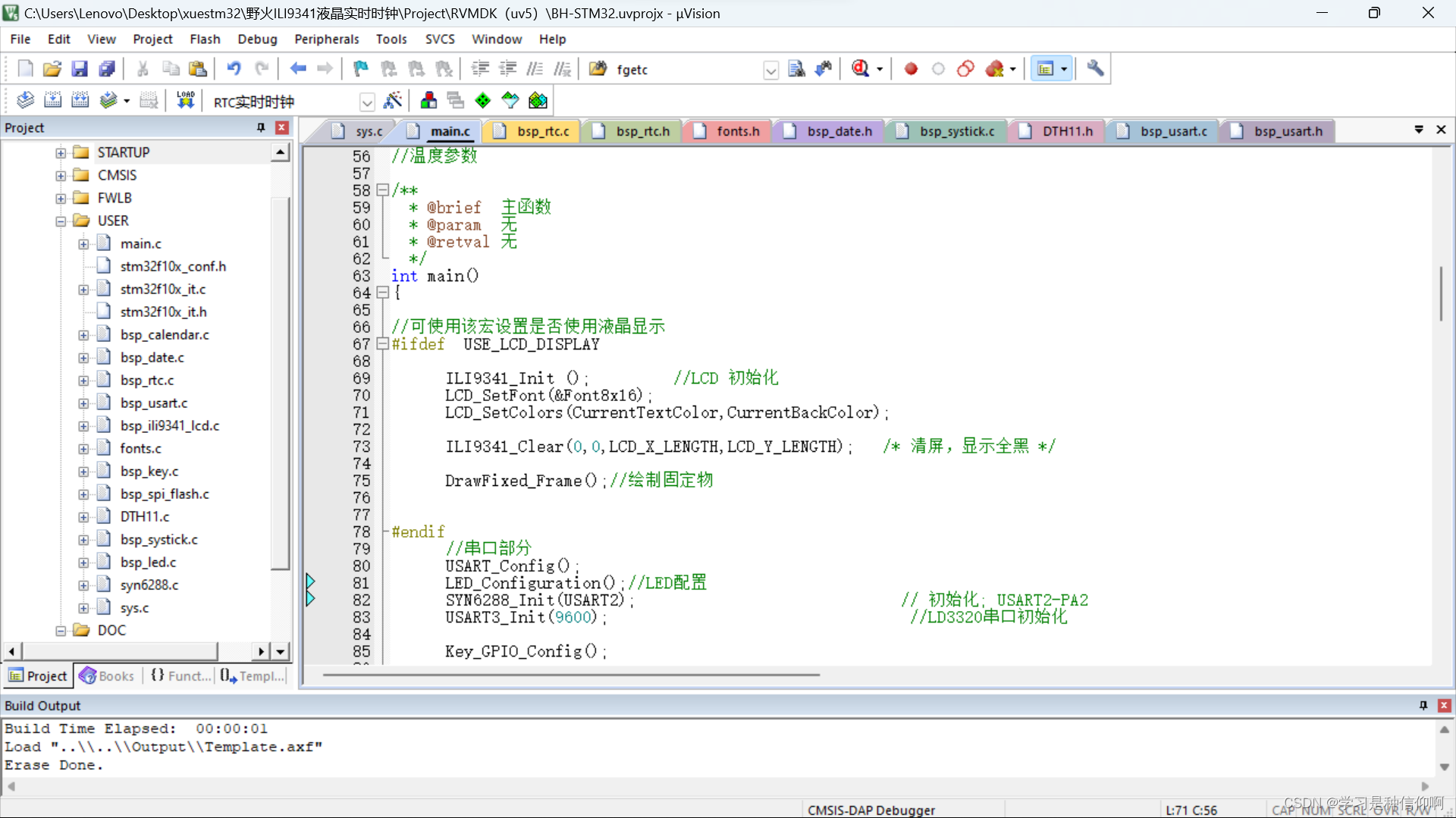

首先创建如下工程目录结构。

and2.v

// 2-input and gate model

module and2 (

input a,

input b,

output y

);

assign y = a & b;

endmoduleand2_tb.v

// Two-input and gate test-bench

`timescale 1s/100ms

`include "and2.v"

module and2_tb();

reg a;

reg b;

wire y;

and2 iand2(a, b, y);

initial begin

$monitor("a=%b, b=%b, y=%b", a, b, y);

$dumpfile("and2.vcd"); // 导出vcd文件

$dumpvars(0, and2_tb); // 导出and2_tb模块中的所有变量

a = 0; b = 0; #10;

a = 0; b = 1; #10;

a = 1; b = 0; #10;

a = 1; b = 1; #10;

$finish;

end

endmodule在vscode终端进行编译

编译后运行and2.out,输出如下:

其中and2.vcd即可用gtkwave工具打开进行波形仿真

打开效果如下

展开and2_tb的变量列表

然后进行波形仿真

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)